|

On-line demos Project manager |

SDL Z.100 SDL-RT |

UML Brochures |

|

|

|||||

|

Editors Import existing SDL systems

RTDS G3 imports SDL description in its textual format called SDL-PR (Phrasal Representation).

Based on the CIF (Common Interchange Format) information it keeps the graphical layout as it was in the

original system. The import mechanism has been tested on very large existing industrial models

(more than 40,000 lines) and PragmaDev is commited to support its customers when importing

legacy code. RTDS G3 also exports SDL in textual format in order to run in any existing tool such as a test generator, exhaustive simulation tool, model checking tool, code generator. SDL editor SDL editor is an easy to use, intuitive interface to design SDL systems. It includes all can be expected of such an editor such as : copy/paste, unlimited undo/redo, automatic symbol insertion. The diagrams include a page setup to guarantee the final diagram will be printable. Diagrams can also be saved as PNG or JPEG files.

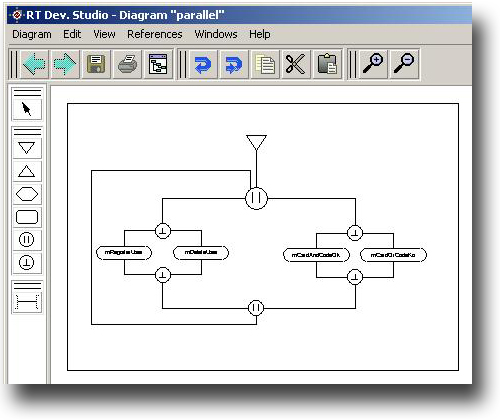

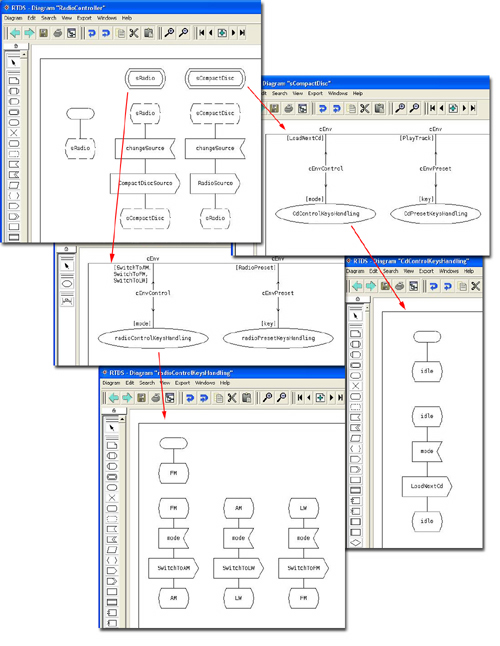

Dynamic graphical traces The Message Sequence Chart (MSC) representation provides a detailed description of the dynamic behaviour of the system. It can be used to specify a behaviour or to trace the simulated system. Each process is seen as a line on the diagram where time flows from top to bottom. Key events in the system have a graphical representation such as: internal states modification, message inputs and outputs with structured parameters, timers, process creations or deletions... MSC diagrams can be organized using the SDL HMSC diagram. HMSC editor High level Message Sequence Chart editor allows to organize MSC diagrams and define how they relate to one another: MSCs can be executed in parallel or in sequence.  First tool on the market to support composite states A composite state is basically a state in which one or several sub-finite state machine are running. An incoming signal is first considered by the super state. If not in the signal set the sub states are the considered. This is a concept that is found in a lot of consumer electronic MMI. A classical example is a car radio where each key has a different meaning depending on the source. The same key will switch from FM to AM when using the radio source; or it might switch to the next CD when using the CD source. The snapshots below describe this basic example.  |

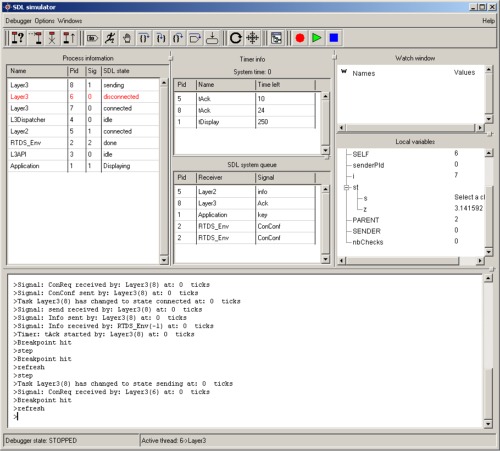

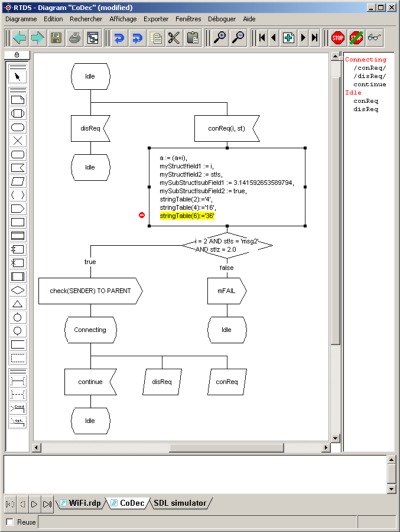

Simulation and code generation Graphical debugging The SDL system can be simulated with the built-in simulator based on SDL semantic to verify the system behavior. Once validated, full code can be generated with RTOS integrations to be implemented on a real target. Whether the SDL system is simulated, or whether the generated C code is debugged on target, the RTDS debugger interface will display all relevant information:

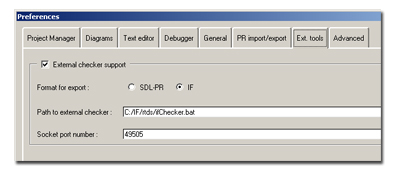

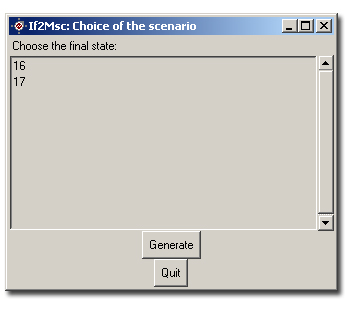

Model checking

It is now possible to export an SDL System to IF form as defined by

Verimag Labs.

|